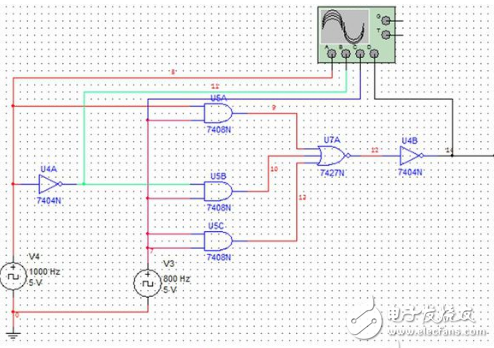

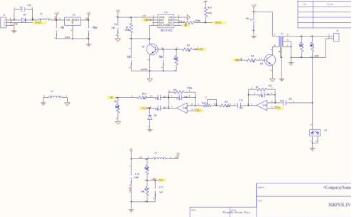

圖1中,V8為振蕩電路產(chǎn)生的振蕩脈沖,其占空比為50%,由該脈沖決定開關(guān)器件的工作頻率。V1為原邊電流采樣電阻上的壓降,V2為輸出電壓的反饋值,V3是用于驅(qū)動開關(guān)管的信號。V2經(jīng)過PI調(diào)節(jié)器進(jìn)行誤差放大后輸入到比較器的反向端,與輸入到比較器同向端的經(jīng)過誤差放大后的V1值進(jìn)行比較,從而決定V3的脈寬大小。邏輯電路產(chǎn)生的信號經(jīng)過輸出級后用來驅(qū)動MOSFET的開通和關(guān)斷,該信號(V3)的占空比與輸出電壓的反饋值V2成反比,實現(xiàn)電壓反饋式的控制環(huán),同時,該信號的占空比還與輸入的直流電壓值成反比,以實現(xiàn)電路的前饋控制。V3信號由經(jīng)過放大后的原邊電流的采樣電阻上的電壓值和經(jīng)過PI調(diào)節(jié)器的輸出電壓的反饋值共同來控制。圖2為各個反饋信號的誤差放大值、振蕩脈沖V8以及MOSFET的驅(qū)動信號V3波形。圖2中1)為振蕩脈沖V8的波形,2)為驅(qū)動信號V3的波形,3)、4)為電壓反饋和電流反饋值經(jīng)過誤差放大后的波形(V2和V1的波形)。

電子發(fā)燒友App

電子發(fā)燒友App

評論