3D Interconnect Technology

審稿人:清華大學(xué) 王喆壵

https://www.tsinghua.edu.cn

審稿人:北京大學(xué) 張興 蔡一茂

https://www.pku.edu.cn

10.5 新型集成與互聯(lián)

第10章 集成電路基礎(chǔ)研究與前沿技術(shù)發(fā)展

《集成電路產(chǎn)業(yè)全書》下冊(cè)

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

集成電路

+關(guān)注

關(guān)注

5453文章

12587瀏覽量

374807

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

集成電路制造中薄膜生長(zhǎng)工藝的發(fā)展歷程和分類

薄膜生長(zhǎng)是集成電路制造的核心技術(shù),涵蓋PVD、CVD、ALD及外延等路徑。隨技術(shù)節(jié)點(diǎn)演進(jìn),工藝持續(xù)提升薄膜均勻性、純度與覆蓋能力,支撐銅互連、高k柵介質(zhì)及應(yīng)變器件發(fā)展。未來將聚焦低溫沉積、三維

【「芯片設(shè)計(jì)基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗(yàn)】--全書概覽

國內(nèi)集成電路設(shè)計(jì)EDA行業(yè)領(lǐng)頭羊一員,以實(shí)事求是、開拓創(chuàng)新,積極進(jìn)取精神 向讀者展現(xiàn)講解,也是在激勵(lì)集成電路EDA產(chǎn)業(yè)不斷發(fā)展壯大,勇立潮頭。

發(fā)表于 01-18 17:50

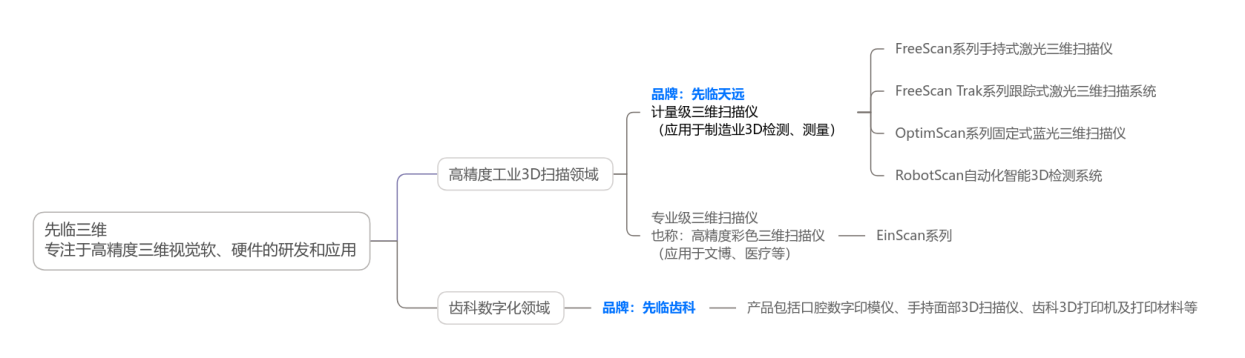

一文讀懂 | 三維視覺領(lǐng)域國家級(jí)制造業(yè)單項(xiàng)冠軍——先臨三維的品牌布局

先臨三維科技股份有限公司成立于2004年,是三維視覺領(lǐng)域國家級(jí)制造業(yè)單項(xiàng)冠軍、國家專精特新“小巨人”企業(yè)。公司專注于高精度三維視覺軟、硬件的研發(fā)和應(yīng)用,致力于成為具有全球影響力的三維視

淺談三維集成封裝技術(shù)的演進(jìn)

在半導(dǎo)體封裝領(lǐng)域,堆疊技術(shù)作為推動(dòng)高集成度與小型化的核心趨勢(shì),正通過垂直堆疊芯片或封裝實(shí)現(xiàn)更緊湊的封裝尺寸及優(yōu)化的電氣性能——其驅(qū)動(dòng)力不僅源于信號(hào)傳輸與功率分布路徑的縮短,更體現(xiàn)在對(duì)系統(tǒng)級(jí)封裝(SiP)與三維集成(3D IC)的

集成電路制造中薄膜刻蝕的概念和工藝流程

薄膜刻蝕與薄膜淀積是集成電路制造中功能相反的核心工藝:若將薄膜淀積視為 “加法工藝”(通過材料堆積形成薄膜),則薄膜刻蝕可稱為 “減法工藝”(通過材料去除實(shí)現(xiàn)圖形化)。通過這一 “減”

?三維集成電路的TSV布局設(shè)計(jì)

在三維集成電路設(shè)計(jì)中,TSV(硅通孔)技術(shù)通過垂直互連顯著提升了系統(tǒng)集成密度與性能,但其物理尺寸效應(yīng)與寄生參數(shù)對(duì)互連特性的影響已成為設(shè)計(jì)優(yōu)化的核心挑戰(zhàn)。

構(gòu)建適用于三維集成系統(tǒng)的互連線長(zhǎng)分布模型

在三維集成電路設(shè)計(jì)中,TSV技術(shù)通過垂直互連顯著優(yōu)化了互連線長(zhǎng)分布特性?;趥愄囟傻慕?jīng)典分析框架,可構(gòu)建適用于三維集成系統(tǒng)的

請(qǐng)幫幫我:AutoCAD三維顯示問題,和人正常視角相背

AutoCAD三維顯示問題,和人正常視角相背

AutoCAD三維顯示問題,和人正常視角相背

發(fā)表于 08-14 09:50

基于TSV的三維集成電路制造技術(shù)

三維集成電路工藝技術(shù)因特征尺寸縮小與系統(tǒng)復(fù)雜度提升而發(fā)展,其核心目標(biāo)在于通過垂直堆疊芯片突破二維物理極限,同時(shí)滿足高密度、高性能、高可靠性及低成本的綜合需求。

VirtualLab:光學(xué)系統(tǒng)的三維可視化

摘要

為了對(duì)光學(xué)系統(tǒng)的性質(zhì)有一個(gè)基本的了解,對(duì)其組件的可視化和光傳播的提示是非常有幫助的。為此,VirtualLab Fusion提供了一個(gè)工具來顯示光學(xué)系統(tǒng)的三維視圖。這些工具可以進(jìn)一步用于檢查

發(fā)表于 05-30 08:45

中國集成電路大全 接口集成電路

資料介紹本文系《中國集成電路大全》的接口集成電路分冊(cè),是國內(nèi)第一次比較系統(tǒng)地介紹國產(chǎn)接口集成電路的系列、品種、特性和應(yīng)用方而知識(shí)的書籍。全書共有總表、正文和附錄

發(fā)表于 04-21 16:33

概倫電子集成電路工藝與設(shè)計(jì)驗(yàn)證評(píng)估平臺(tái)ME-Pro介紹

ME-Pro是概倫電子自主研發(fā)的用于聯(lián)動(dòng)集成電路工藝與設(shè)計(jì)的創(chuàng)新性驗(yàn)證評(píng)估平臺(tái),為集成電路設(shè)計(jì)、CAD、工藝開發(fā)、SPICE模型和PDK專業(yè)從業(yè)人員提供了一個(gè)共用平臺(tái)。

CMOS集成電路的基本制造工藝

本文主要介紹CMOS集成電路基本制造工藝,特別聚焦于0.18μm工藝節(jié)點(diǎn)及其前后的變化,分述如下:前段工序(FrontEnd);0.18μmCMOS前段工序詳解;0.18μmCMOS后段鋁互連

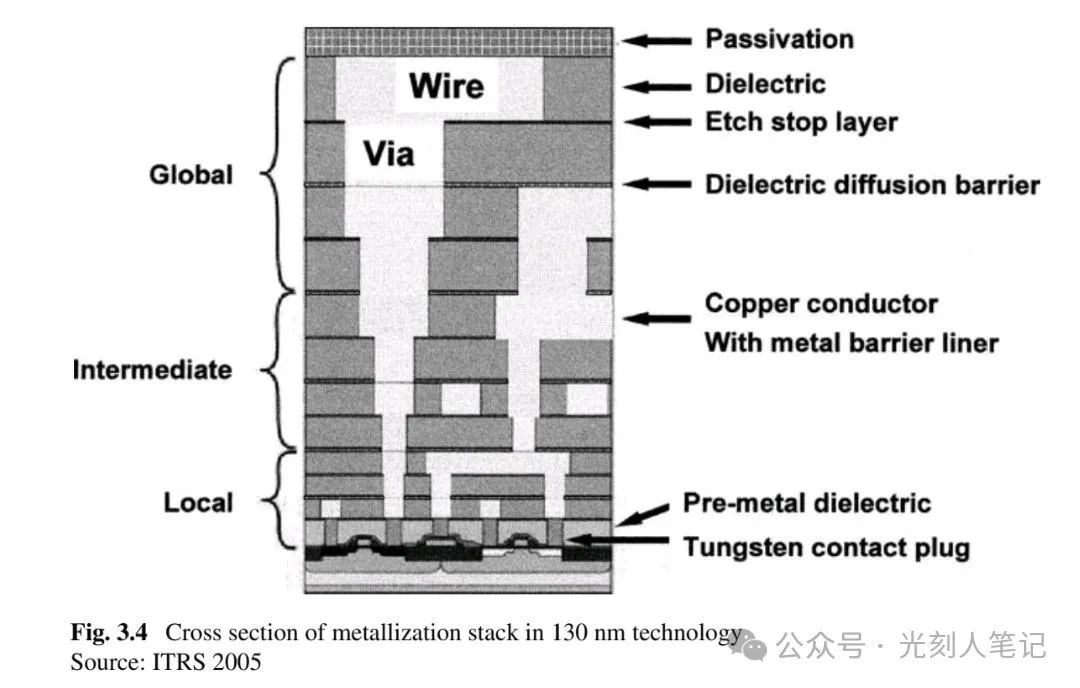

10.5.1 三維互連工藝∈《集成電路產(chǎn)業(yè)全書》

10.5.1 三維互連工藝∈《集成電路產(chǎn)業(yè)全書》

評(píng)論