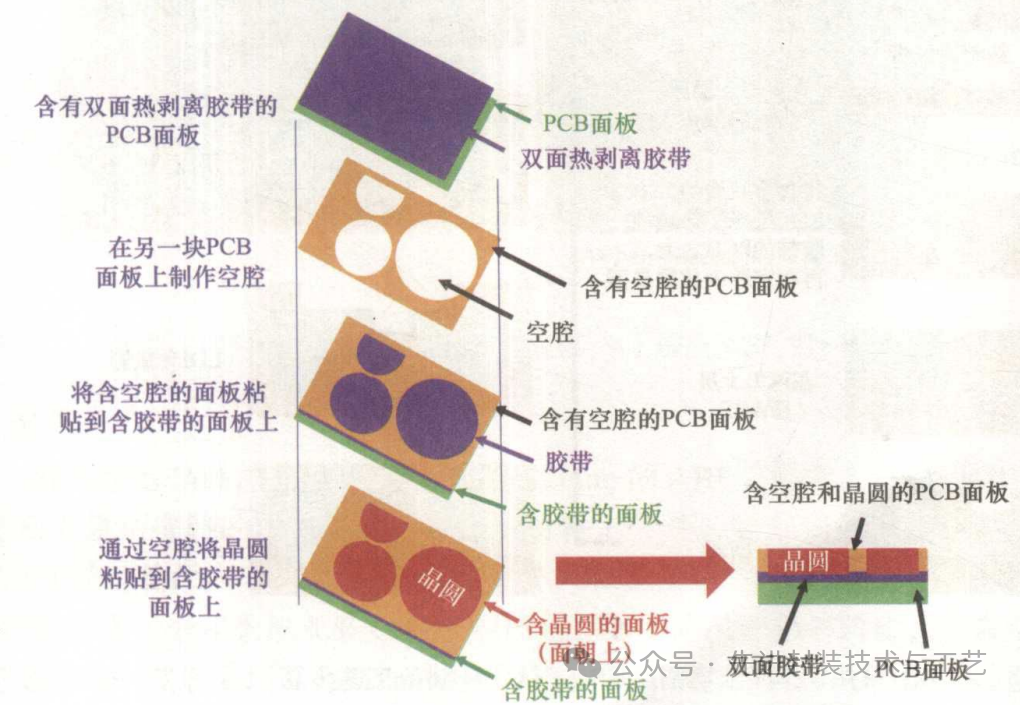

晶圓級(jí)扇出型封裝的三大核心工藝流程

在后摩爾時(shí)代,扇出型晶圓級(jí)封裝(FOWLP) 已成為實(shí)現(xiàn)異構(gòu)集成、提升I/O密度和縮小封裝尺寸的關(guān)鍵....

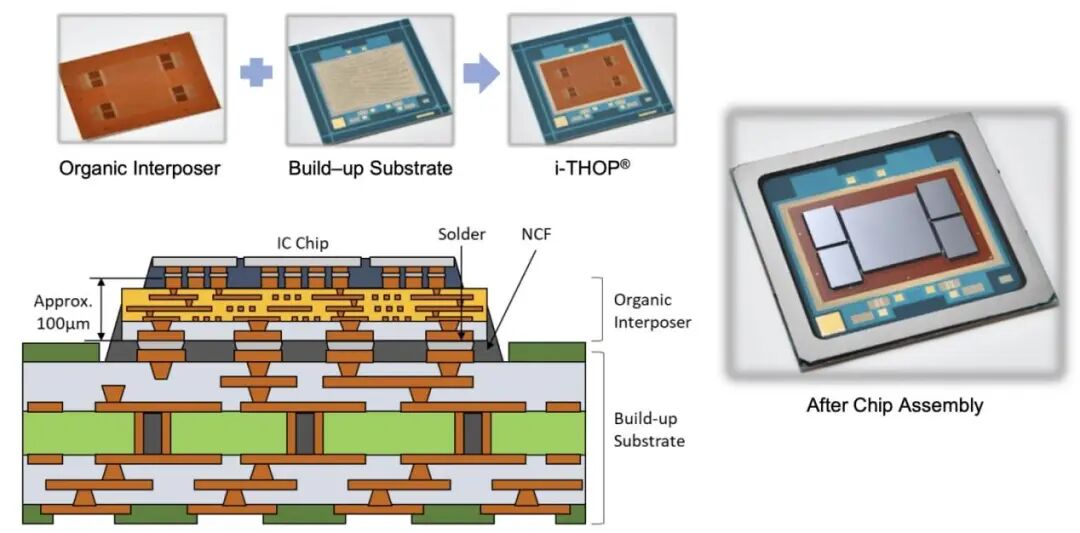

多Chiplet異構(gòu)集成的先進(jìn)互連技術(shù)

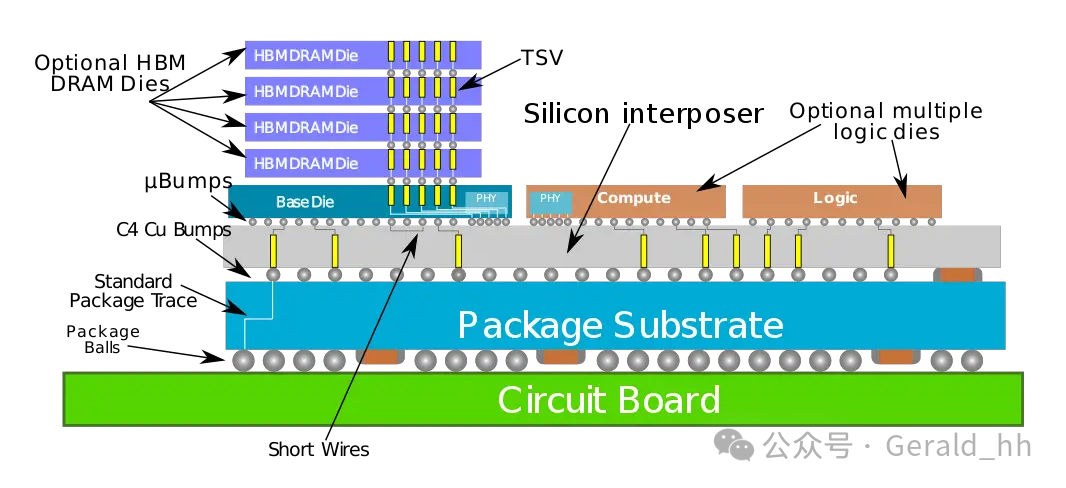

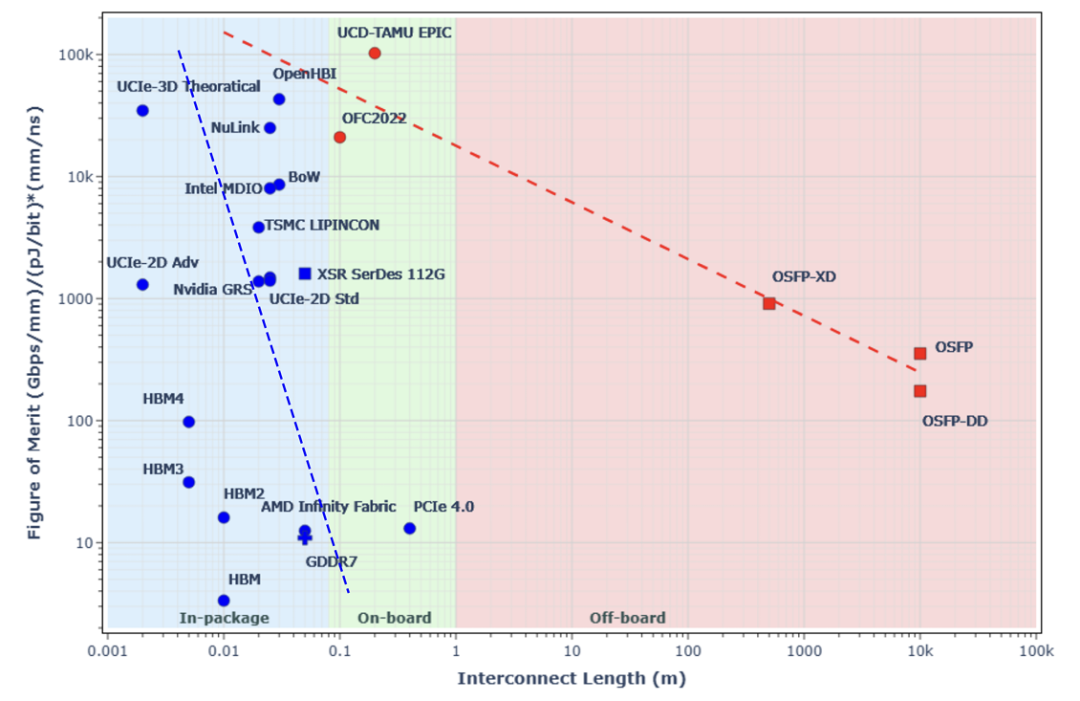

半導(dǎo)體產(chǎn)業(yè)正面臨傳統(tǒng)芯片縮放方法遭遇基本限制的關(guān)鍵時(shí)刻。隨著人工智能和高性能計(jì)算應(yīng)用對(duì)計(jì)算能力的需求....

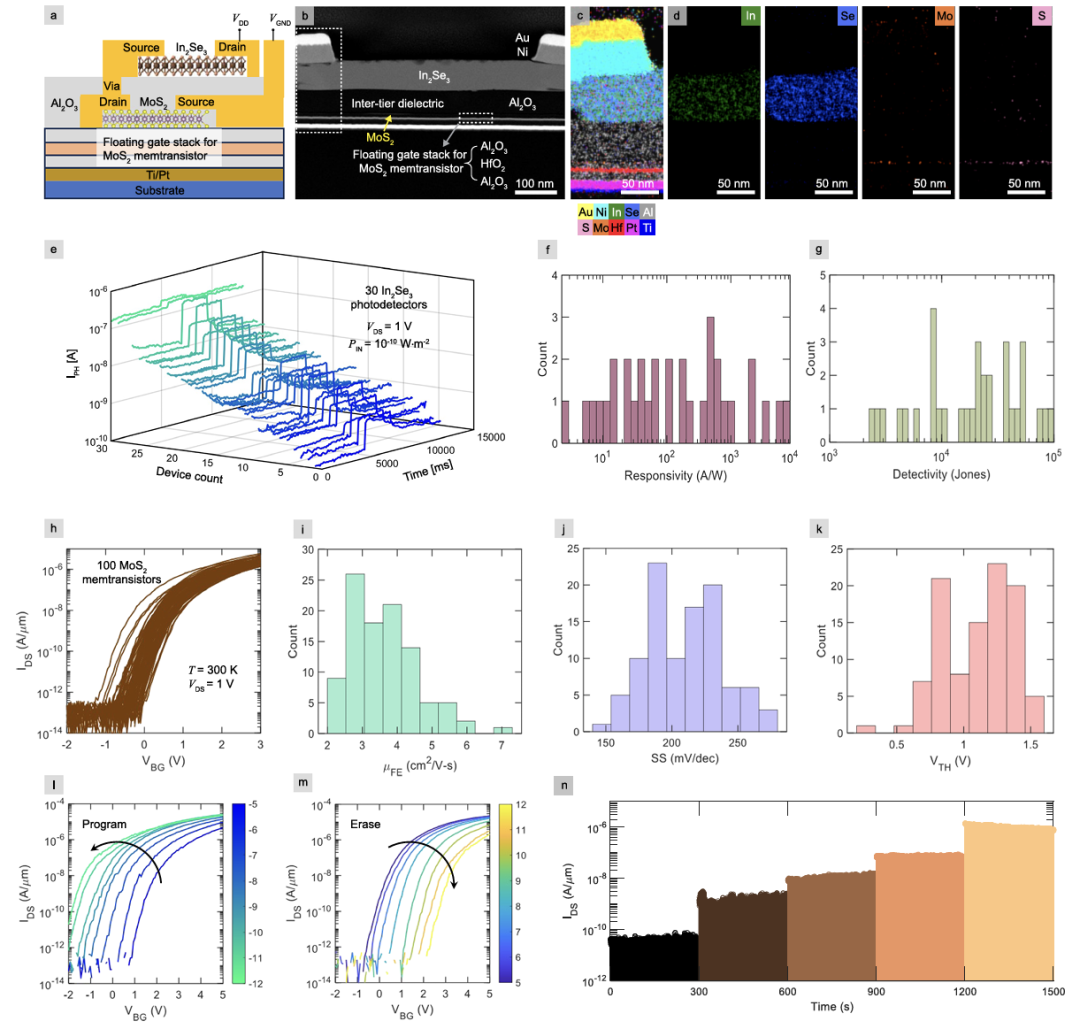

2D材料3D集成實(shí)現(xiàn)光電儲(chǔ)備池計(jì)算

先進(jìn)材料與三維集成技術(shù)的結(jié)合為邊緣計(jì)算應(yīng)用帶來了新的可能性。本文探討研究人員如何通過單片3D集成方式....

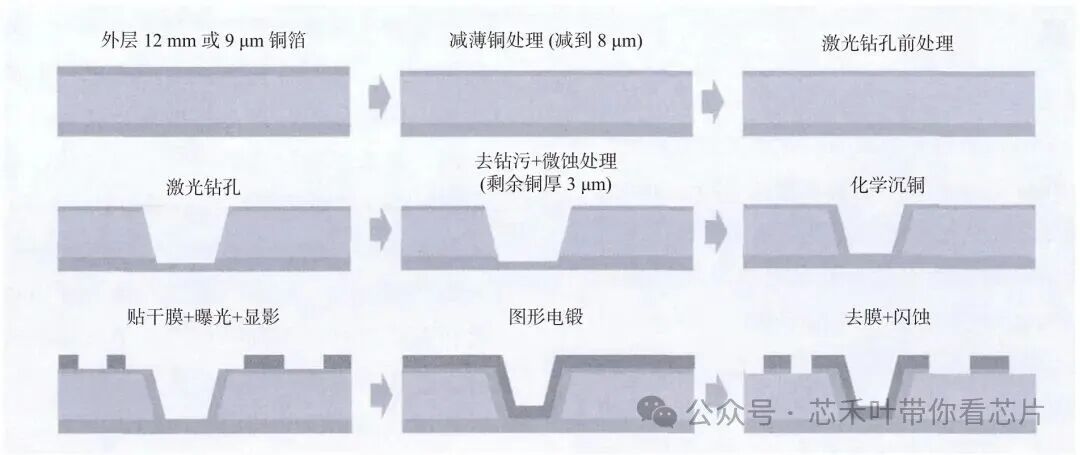

一文詳解封裝基板的制備工藝

在封裝基板發(fā)展的早期階段,廣泛采用一種稱為減成法的印制電路板制造技術(shù),亦稱蝕刻銅箔技術(shù)。該技術(shù)的基本....

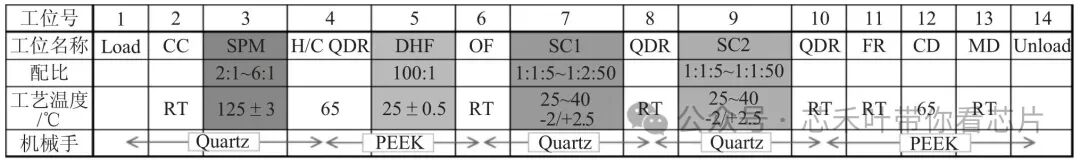

集成電路制造中常用濕法清洗和腐蝕工藝介紹

集成電路濕法工藝是指在集成電路制造過程中,通過化學(xué)藥液對(duì)硅片表面進(jìn)行處理的一類關(guān)鍵技術(shù),主要包括濕法....

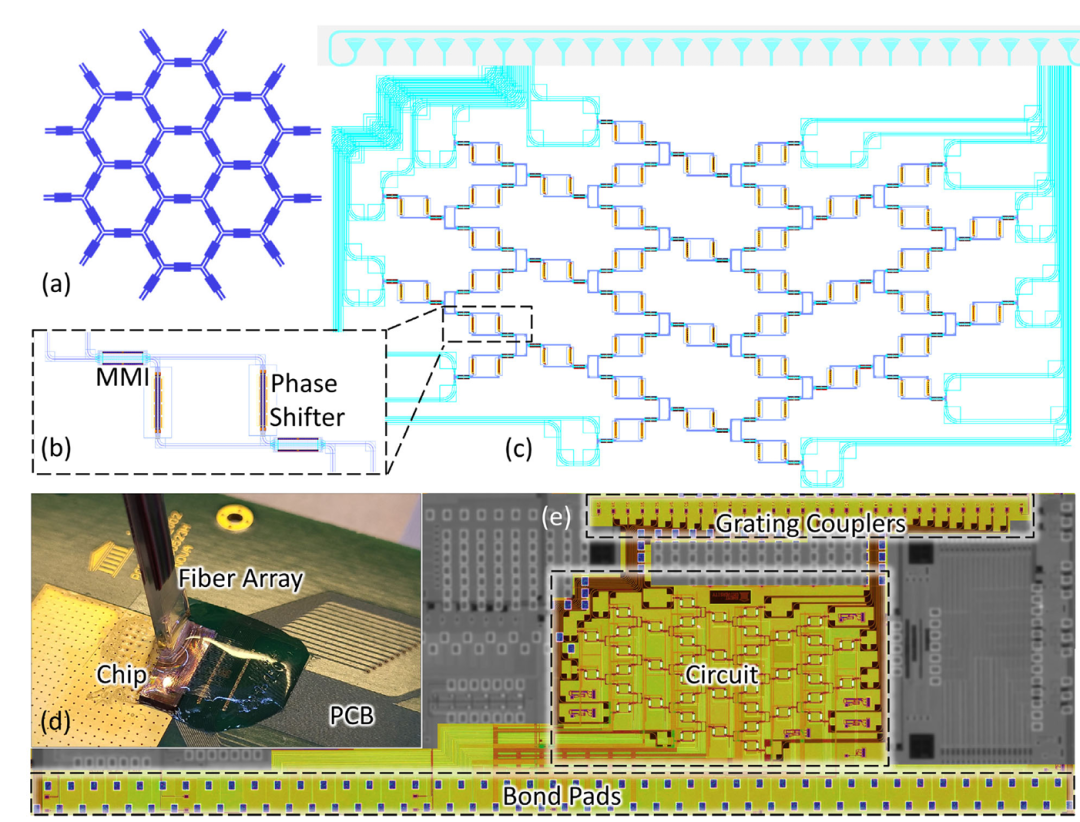

基于六邊形波導(dǎo)網(wǎng)格架構(gòu)實(shí)現(xiàn)可編程光子技術(shù)

硅基光電子技術(shù)的發(fā)展催生了可編程光電子集成芯片的誕生,這類芯片可以通過軟件重新配置來實(shí)現(xiàn)多種應(yīng)用功能....

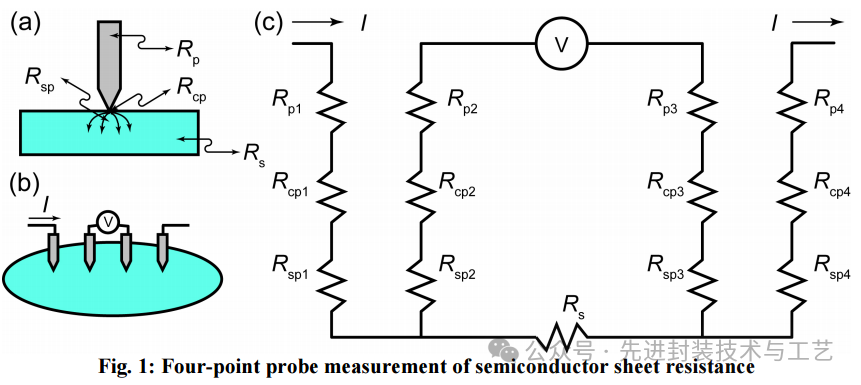

四探針法測(cè)量半導(dǎo)體薄層電阻的原理解析

在半導(dǎo)體材料與器件的表征中,薄層電阻是一個(gè)至關(guān)重要的參數(shù),直接關(guān)系到導(dǎo)電薄膜、摻雜層以及外延層的電學(xué)....

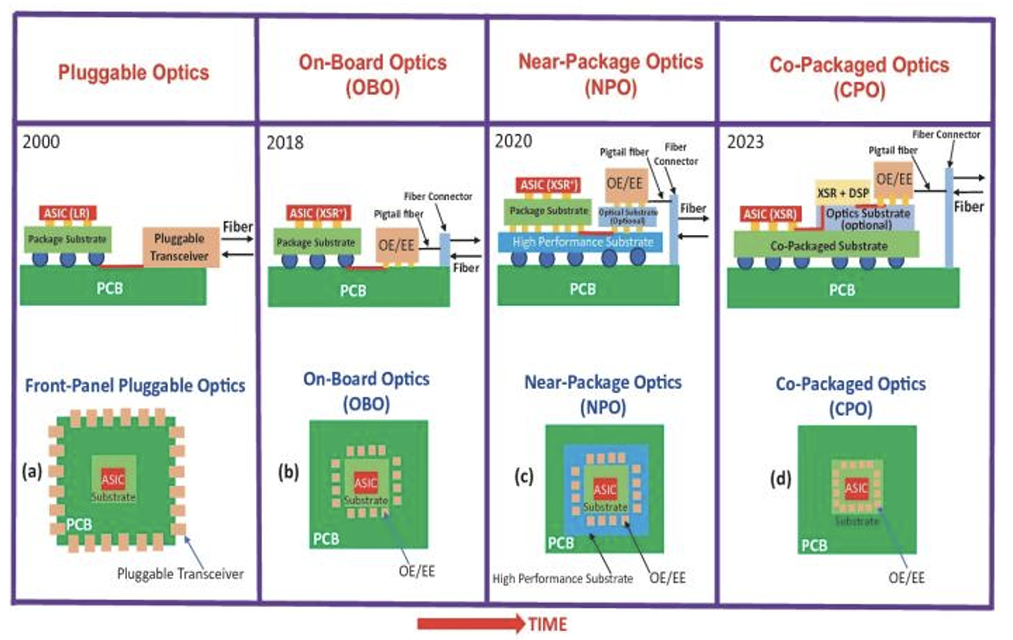

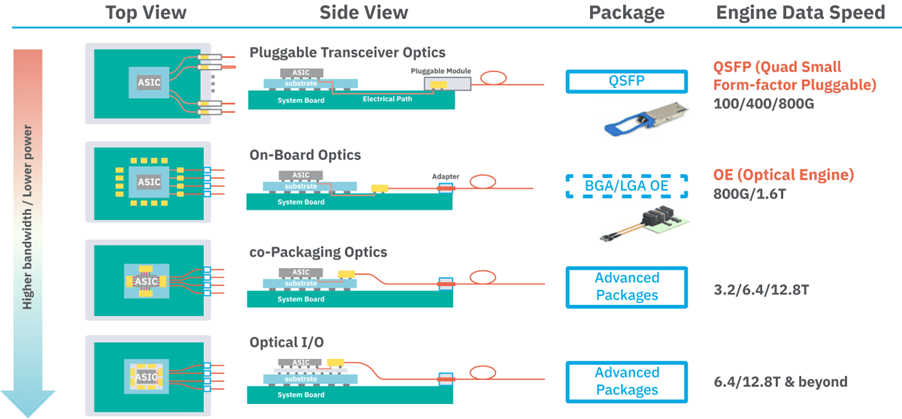

從可插拔模塊到光電共封裝技術(shù)的演進(jìn)

人工智能、云計(jì)算和高性能計(jì)算的快速發(fā)展對(duì)現(xiàn)代數(shù)據(jù)中心的數(shù)據(jù)傳輸帶寬和能源效率提出了更高的要求。傳統(tǒng)的....

扇出型晶圓級(jí)封裝技術(shù)的概念和應(yīng)用

扇出型晶圓級(jí)封裝(FOWLP)的概念最早由德國英飛凌提出,自2016 年以來,業(yè)界一直致力于FOWL....

人工智能加速先進(jìn)封裝中的熱機(jī)械仿真

為了實(shí)現(xiàn)更緊湊和集成的封裝,封裝工藝中正在積極開發(fā)先進(jìn)的芯片設(shè)計(jì)、材料和制造技術(shù)。隨著具有不同材料特....

一文詳解3D光電互連技術(shù)

人工智能和機(jī)器學(xué)習(xí)應(yīng)用的爆炸式增長(zhǎng)已經(jīng)將高性能計(jì)算系統(tǒng)推向極限。在訓(xùn)練日益復(fù)雜的AI模型時(shí),計(jì)算需求....

臺(tái)積電CoWoS平臺(tái)微通道芯片封裝液冷技術(shù)的演進(jìn)路線

臺(tái)積電在先進(jìn)封裝技術(shù),特別是CoWoS(Chip on Wafer on Substrate)平臺(tái)上....

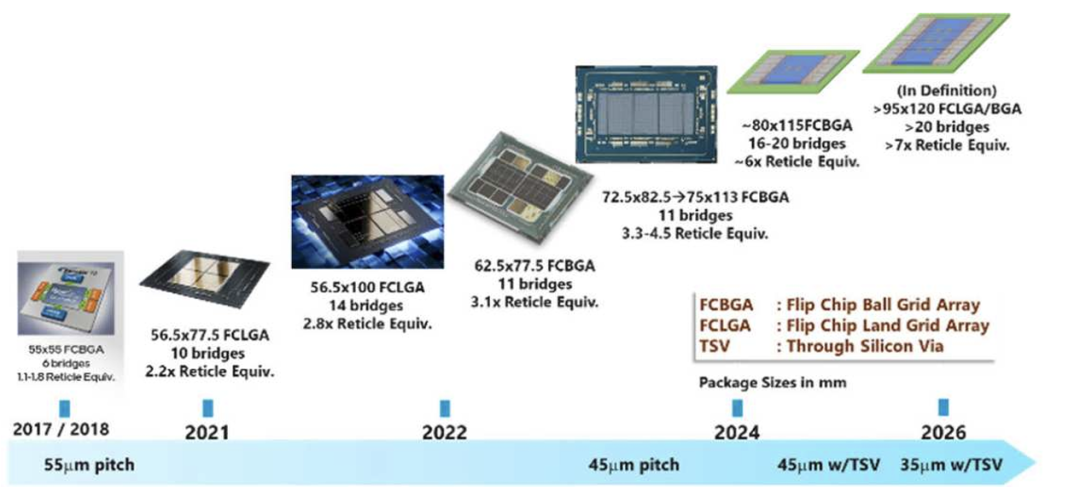

Chiplet與異構(gòu)集成的先進(jìn)基板技術(shù)

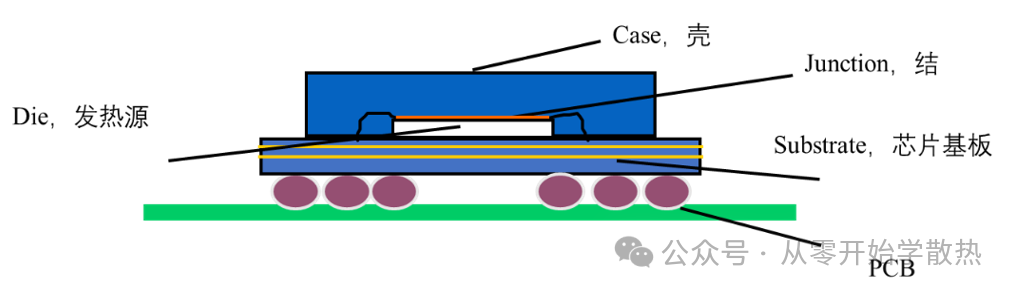

半導(dǎo)體產(chǎn)業(yè)正處在傳統(tǒng)封裝邊界逐步消解的轉(zhuǎn)型節(jié)點(diǎn),新的集成范式正在涌現(xiàn)。理解從分立元件到復(fù)雜異構(gòu)集成的....

玻璃基板技術(shù)的現(xiàn)狀和優(yōu)勢(shì)

玻璃基板正在改變半導(dǎo)體封裝產(chǎn)業(yè),通過提供優(yōu)異的電氣和機(jī)械性能來滿足人工智能和高性能計(jì)算應(yīng)用不斷增長(zhǎng)的....

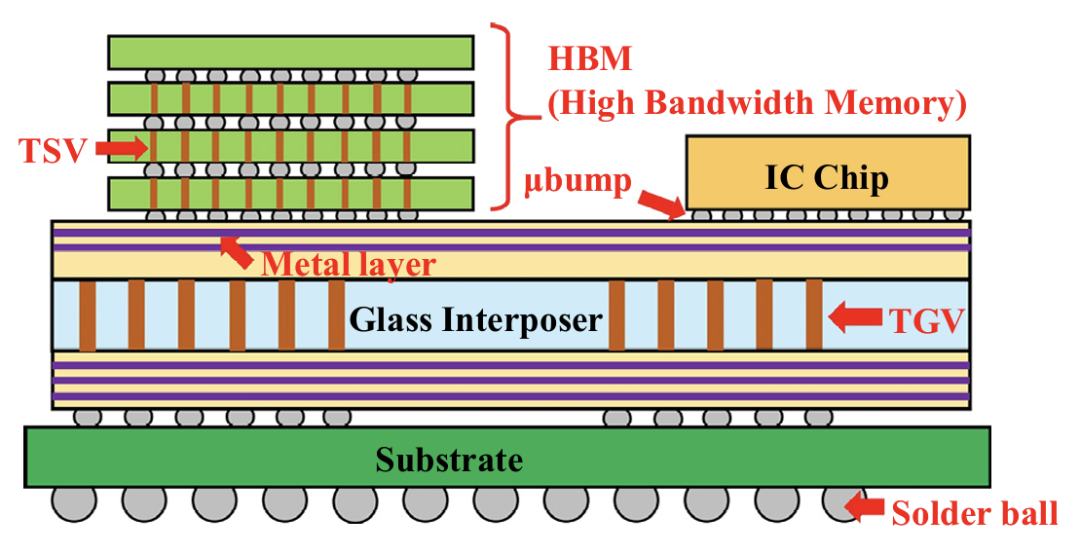

玻璃中介板技術(shù)的結(jié)構(gòu)和性能優(yōu)勢(shì)

半導(dǎo)體行業(yè)持續(xù)推進(jìn)性能和集成度的邊界,Chiplet技術(shù)作為克服傳統(tǒng)單片設(shè)計(jì)局限性的解決方案正在興起....

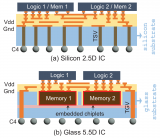

簡(jiǎn)單認(rèn)識(shí)CoWoP封裝技術(shù)

半導(dǎo)體行業(yè)正面臨傳統(tǒng)封裝方法的性能極限,特別是在滿足AI計(jì)算需求的爆炸性增長(zhǎng)方面。CoWoP(芯片晶....

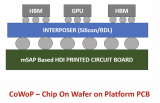

詳解先進(jìn)封裝中的混合鍵合技術(shù)

在先進(jìn)封裝中, Hybrid bonding( 混合鍵合)不僅可以增加I/O密度,提高信號(hào)完整性,還....

用于高性能半導(dǎo)體封裝的玻璃通孔技術(shù)

半導(dǎo)體行業(yè)正在經(jīng)歷向更緊湊、更高效封裝解決方案的轉(zhuǎn)型。隨著移動(dòng)設(shè)備和物聯(lián)網(wǎng)(IoT)應(yīng)用對(duì)更小、更薄....

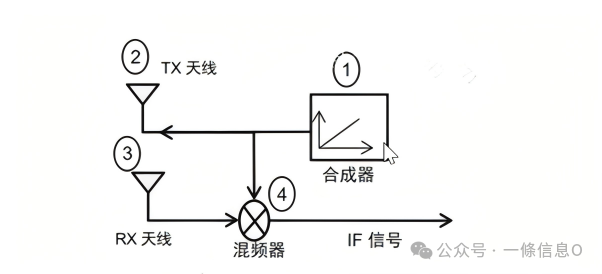

光電共封裝技術(shù)的實(shí)現(xiàn)方案

數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu)正在經(jīng)歷向光電共封裝(CPO)交換機(jī)的根本性轉(zhuǎn)變,這種轉(zhuǎn)變主要由其顯著的功耗效率優(yōu)勢(shì)....

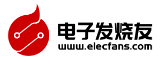

先進(jìn)Interposer與基板技術(shù)解析

傳統(tǒng)封裝方法已無法滿足人工智能、高性能計(jì)算和下一代通信技術(shù)的需求。晶體管尺寸已縮小至個(gè)位數(shù)納米量級(jí),....

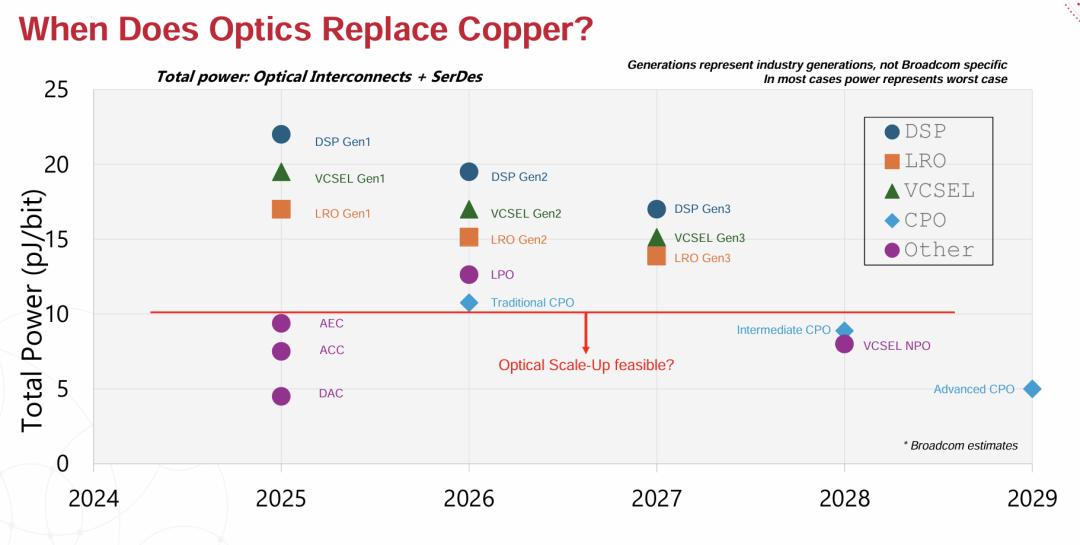

Broadcom光電共封裝技術(shù)解析

光電共封裝(Co-Packaged Optics,CPO)代表了光互連技術(shù)的新發(fā)展方向,這種技術(shù)將光....

FOPLP工藝面臨的挑戰(zhàn)

FOPLP 技術(shù)目前仍面臨諸多挑戰(zhàn),包括:芯片偏移、面板翹曲、RDL工藝能力、配套設(shè)備和材料、市場(chǎng)應(yīng)....

基于硅基異構(gòu)集成的BGA互連可靠性研究

在異構(gòu)集成組件中,互連結(jié)構(gòu)通常是薄弱處,在經(jīng)過溫度循環(huán)、振動(dòng)等載荷后,互連結(jié)構(gòu)因熱、機(jī)械疲勞而斷裂是....